Faculty at School of Engineering

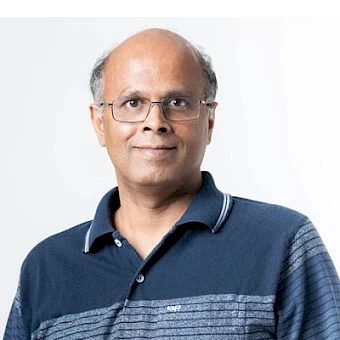

Venkatnarayan Hariharan

Associate Professor

School of Engineering

Associate Professor

School of Engineering